Intel's Atom Architecture: The Journey Begins

by Anand Lal Shimpi on April 2, 2008 12:05 AM EST- Posted in

- CPUs

Lower Power than Centrino

(This page is taken from our earlier look at the Intel Atom architecture)

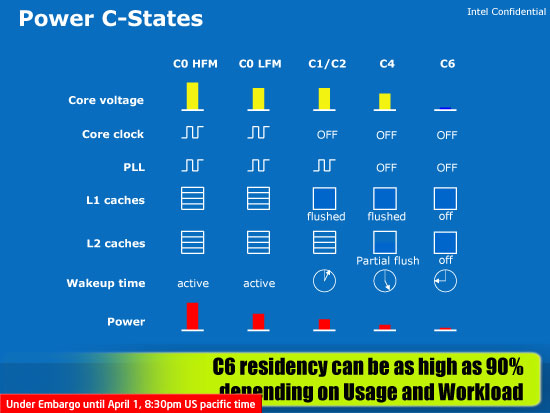

With mobile Penryn Intel introduced a new power state it calls C6. In the C6 power state the CPU is in a virtual reset state, and core voltage is very close to zero. The core clock, all of the PLLs, and caches are completely turned off. All of the state data is saved in a 10.5KB storage area, similar to mobile Penryn (but smaller since there's not as much state to save). Upon exiting C6 the processor's previous state is restored from this memory, called the C6 array. It takes around 100us to get out of C6, but the power savings are more than worth the effort - it's a similar approach of power for performance that we saw in the design of the original Pentium M processor.

Clock gating (sending the clock signal through a logic gate that can disable it on the fly, thus shutting off whatever the clock connects to) is an obvious aspect of Atom's design. All Intel processors use clock gating; Atom simply uses it more aggressively - the clock going to every "power zone" is gated, something that isn't the case in mobile Core 2. Each logic cluster (205 total) in Atom is referred to as a Functional Unit Block (FUB) and the entire chip uses what Intel calls a sea of FUB design. Each FUB is clock gated and can be disabled independently to optimize for power consumption. The cache in Atom is in its own FUB, which apparently isn't the case in mobile Core 2.

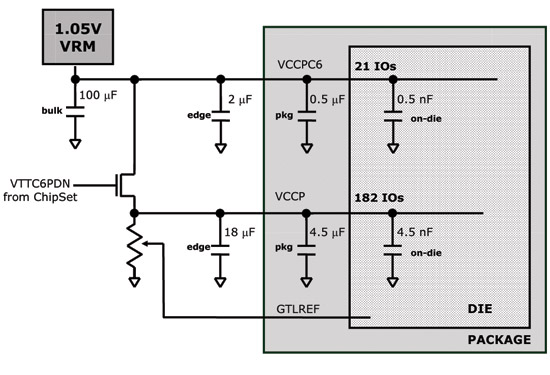

Keeping Silverthorne on life support, only 21 pins are necessary

Atom uses a split power plane; in its deepest sleep state (C6) the chip can shut off all but 21 pins which are driven by the 1.05V VRM. By having two separate power planes the chip can manage power on a more granular level. While it can't disable individual pins, it can disable large groups of them leaving only 21 active when things like the L2 cache and bus interface are powered down.

Intel mentioned that Atom will remain in its C6 sleep state 90% of the time. However, that figure is slightly misleading because it's only possible to remain in C6 when the CPU is completely idle. The 90% figure comes from taking into account a mobile device sitting in your pocket doing nothing most of the time. When in use, Atom won't be able to spend nearly that much time in C6.

Despite the implementation of a C6 power state, Atom will still lose to ARM based processors in both active and idle power. The active power disadvantage will be erased over the coming years as the microarchitecture evolves (and smaller manufacturing processes are implemented), while the idle power requires more of a platform approach. As we reported in our first Menlow/Silverthorne article:

"The idle power reduction will come through highly integrated platforms, like what we're describing with Moorestown. By getting rid of the PCI bus and replacing it with Intel's own custom low-power interface, Intel hopes to get idle power under control. The idea is that I/O ports will only be woken up when needed (similar to how the data lines on the Centrino FSB function), and what will result are platforms with multiple days of battery life when playing back music."

46 Comments

View All Comments

lopri - Thursday, April 3, 2008 - link

This article is as much propagana-ish as it is technical. Did you read the last page of the article?clnee55 - Friday, April 4, 2008 - link

Since Anand wrote this article. I let him answer your accusationGulWestfale - Wednesday, April 2, 2008 - link

i believe that the graphics core in the chipset is a powerVR gen5 derivative; intel already uses some of their tech in its existing mainboards and wikipedia states that intel has licensed gen5 tech for one of its chipsets, the GMA500 (which is the same as poulsbo?) gen5 is also DX10-capable, which matches the info in your article.http://en.wikipedia.org/wiki/PowerVR#Series_5_.28S...">http://en.wikipedia.org/wiki/PowerVR#Series_5_.28S...

yyrkoon - Wednesday, April 2, 2008 - link

and wikipedia has been known to be wrong . . . a lot lately it seems.My point here *is*, I would probably trust anandtech more than wikipedia now days, as it seems any Joe can put up a 'reference' without citation.

jones377 - Wednesday, April 2, 2008 - link

Following the references link from the Wiki article...http://www.imgtec.com/News/Release/index.asp?NewsI...">http://www.imgtec.com/News/Release/index.asp?NewsI...

Poulsbo uses a PowerVR 3D core

Anand Lal Shimpi - Wednesday, April 2, 2008 - link

Yep, you guys are correct, I wasn't aware that it was public yet :) I've updated the article.Take care,

Anand