An Introduction to Semiconductor Physics, Technology, and Industry

by Joshua Ho on October 9, 2014 3:00 PM EST- Posted in

- Semiconductors

- CMOS

- Physics

- Industry

- Technology

Improving Transistor Performance

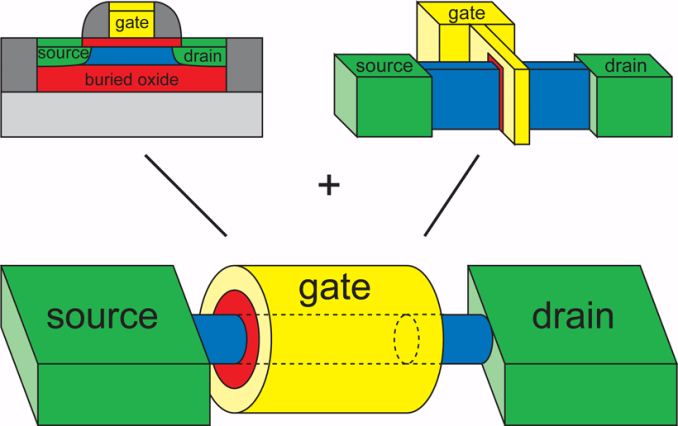

While it's impossible to predict what the future will hold, it's relatively easy to see what trends will take place in the near future to keep Moore's law alive. For example, instead of using dual or tri gate technologies (FinFET), it's reasonable to expect that gate-all-around (GAA) will become the next step in the evolution of transistor shapes. However, it's currently not clear when this would reach mass production, if ever.

Currently, experimental GAAFETs have only existed for around eight years. For reference, FinFETs were first made in 1999. It took around a decade and a half for any such 3D transistor to reach mass production. By continuing to scale to higher k dielectrics for the gate, lower k dielectrics between interconnects, lower resistance metals for interconnects, and even better strain engineering, we will continue to see the scaling of CMOS technology.

CNFET / Joerg Appenzeller

Unfortunately, all of these can only go so far. Fundamentally, there will be a point where silicon-based transistors cannot scale any further. Gate oxides, channel lengths, and other critical dimensions can only shrink so much before either resistance is too high or a myriad of other effects render smaller sizes infeasible.

The next step is almost impossible to predict. Perhaps graphene will take the place of silicon, but graphene currently is impossible to mass-produce and is a semi-metal, which means that it inherently lacks a band gap, although it's possible to create one. While it's been shown that semi-metal transistor logic is possible, it's currently in the very early stages and Boolean logic may be impossible with graphene. Phosphorene has promise as a semiconductor replacement for silicon, but it's similarly impossible to mass produce. Phosphorene-based FETs are still in the exploratory stages, with no actual transistor created yet.

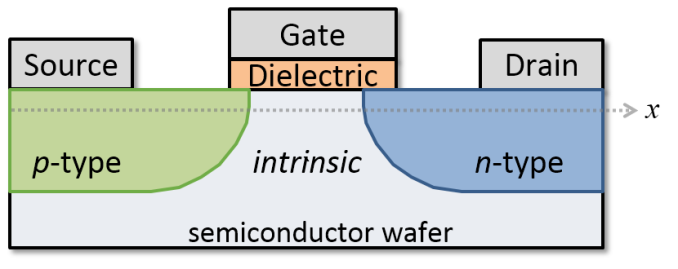

TFET Lateral Structure / Jteherani / CC BY SA

Outside of material changes, the working mechanism of the transistor itself may change. One promising candidate right now is the tunnel field effect transistor, which relies on band to band tunneling rather than the traditional inversion layer generation for current flow. This is similar to leakage that occurs from halo doping, which results from the conduction band of the channel material aligning with the valence band of the source or drain material. As seen by the photo above, this type of transistor has an undoped body and the source/drain are of opposing types. The gate structure is unchanged from previous MOSFETs. In practice, such a transistor structure has a much higher rate of current increase per unit of voltage.

Final Words

It's been a long road, but let's quickly go over the topics covered in this article. We started with a description of semiconductor physics, then moved to the basics of MOSFETs and CMOS. Once we understood how MOSFETs work in CMOS to create logic, we moved on to the actual fabrication process of these transistors in a chip.

After all of this, we discussed how companies have increased the resolution of the fabrication process to make ever smaller transistors, and we continued by looking at how companies have increased transistor performance despite significant engineering challenges. Then we briefly covered what the future may hold for improving device performance and continuing to improve the lithography process to continue making smaller transistors.

But there is far more to be done, as literally everything we write about at AnandTech depends upon ever faster, smaller, and more efficient transistors packed as tightly as possible. Without this continued innovation, the PC, smartphone, and wearables that we see today would be impossible to make. However, continuing the scaling that we have seen within the past decades will require more ingenuity and resources than ever before to continue pushing the limits of what's possible.

Normally, we would end things here, but this time I'd like to end by thanking everyone that has helped make this article possible. It has taken weeks of research and asking questions to get to this point, and I'm sure that without help it would have taken months. Out of the many that have helped, I'd like to specifically thank Chenming Hu, a professor in the graduate school at UC Berkeley and the lead researcher in FinFET and UTB-SOI/FD-SOI, for taking the time to help clarify the reasons for SOI and FinFET. I'd also like to thank Gerd Grau, a doctoral candidate in the graduate school at UC Berkeley, and Intel's TMG for answering all kinds of questions about solid state physics in general.

77 Comments

View All Comments

PrayForDeath - Thursday, October 9, 2014 - link

Articles like this are the reason why I visit Anandtech *starts reading*monstercameron - Thursday, October 9, 2014 - link

Most of this is abit over my head. If possible maybe next time use literary devices to explain these technologies. Also what about tsv and stacked dice?Homeles - Thursday, October 9, 2014 - link

Is there anything in particular you're struggling with?Kutark - Sunday, October 12, 2014 - link

I'm with him. I need someone to take some paper and some crayons and draw me a picture hahaha.climber07 - Monday, October 13, 2014 - link

It isn't an easy concept to grasp at first. Transistors generally operate in two states. On and off. They require a certain voltage to make them come on. For the sake of simplicity, these two states are 1's and 0's (data bits). They form logic gates in circuits (if this and this or this then it equals this). The material that they use for transistors (and diodes) are silicon. Silicon requires approximately .7 volts to forward bias (allow current to flow and turn on). There are literally thousands of websites and graphic representations of basic transistor theory to explore. Try "How Stuff Works dot com".Burn2learn - Friday, November 14, 2014 - link

How can this be over your head if your aware of thru silicon vias (tsv)adityarjun - Thursday, October 9, 2014 - link

Awesome! Hope to see a lot more of such articles for learners.seanleeforever - Thursday, October 9, 2014 - link

pretty much a brief review of my E.E college course back in the days.great article.

A5 - Thursday, October 9, 2014 - link

Yep. Getting bad SRH equation flashbacks now :-pjjj - Thursday, October 9, 2014 - link

Just took a quick look at the article for now so maybe i've missed it but i don't think you mention 3D at all (actual 3D not FinFET or 2.5D packaging).And here comes the crazy question, was looking at the CMOS Chip Structure pic and wondered if anyone has tried to make curved (on 1 or even 2 axis) chips just to have more room on the extremal layers. As i wrote this i remembered the Sony curved image sensor and i wonder how would they fab that if they actually make it into a real product.Any clue?