Phison’s Next-Gen eSSD Controllers to Support Everspin’s STT-MRAM Caching

by Anton Shilov on July 25, 2019 10:00 AM EST

Phison and Everspin on Wednesday said that the former's upcoming controllers for enterprise-grade SSDs would natively support the latter’s spin torque transfer MRAM (STT-MRAM) that will be used as a write buffer to enable a more effective I/O management. The new technology will allow makers of SSDs to improve I/O performance of their drives and enable power loss protection without usage of supercapacitors.

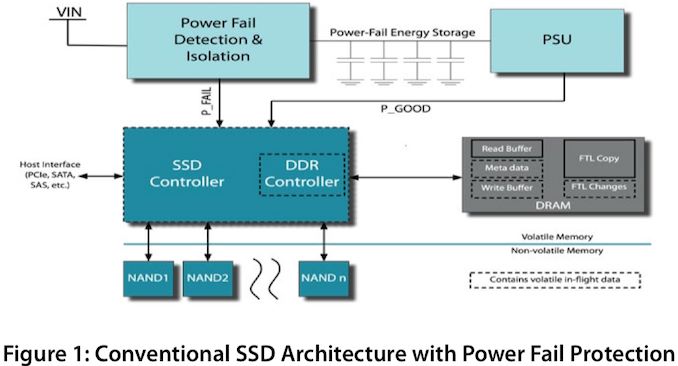

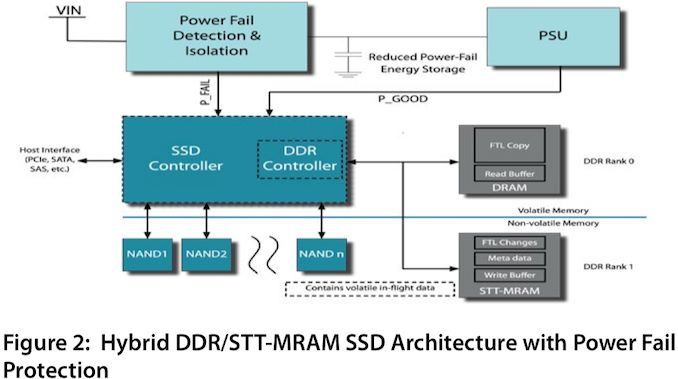

The upcoming eSSD controllers from Phison will support Everspin’s 1 Gb STT-MRAM memory “to increase the reliability and performance” of next-gen server-grade SSDs. In particular, the companies say that STT-MRAM chips will enable SSD makers to more effectively manage I/O streams, which will enable for better latency determinism and therefore improve QoS. Besides, since STT-MRAM is nonvolatile, drives that will use it instead of traditional DRAM buffers will not need a sophisticated power loss protection enabled by supercapacitors, which will simplify their physical architecture and will enable to increase their capacity by adding more 3D NAND packages.

As far as performance of STT-MRAM-enabled SSDs is concerned, the buffer and appropriate software can lower overall latency and increase random performance of drives significantly versus typical SSDs. It is of course too early to say anything about SSDs based on next-generation controllers from Phison, but the partnership between the two companies promises to bring significant performance enhancements to upcoming storage subsystems.

Phison’s SSD partners won't the first to use STT-MRAM as write cache buffers for 3D NAND-based SSDs. Both IBM and Seagate already offer appropriate drives commercially today. Meanwhile, native support of STT-MRAM by SSD controllers will make it considerably cheaper and easier for drive makers to build such products.

Phison and Everspin will discuss use cases of STT-MRAM in enterprise storage applications at Flash Memory Summit in early August.

Related Reading:

- Everspin Begins Production of 1Gb STT-MRAM

- IBM And Everspin Announce 19TB NVMe SSD With MRAM Write Cache

- Seagate Demos New SSD Features And Prototypes At FMS

- Everspin Announces New MRAM Products And Partnerships

Source: Phison

20 Comments

View All Comments

Dragonstongue - Thursday, July 25, 2019 - link

sweet, wonder the cost to include this vs other "conventional" ways of getting the same thing?can that Intel/Micron thing be used in the same fashion, if yes, why has not Intel done "similar" as I doubt they can sell every one of theirs for the prices they want/need to sell at, to use X as a write buffer vs Dram to do the same, I wonder if it is all positives or???

azfacea - Thursday, July 25, 2019 - link

i think the current mram chips are more expensive than capacitors to flush dram. but mram is improving a lot and maybe it will be cheaper eventuallySamus - Friday, July 26, 2019 - link

I think the footprint advantage is what they are going for here. Integrating the functionality of capacitors AND a memory buffer into a single significantly smaller component is a huge boon for NGFF drives.Likewise, there will be no cost advantage because buffers and capacitors are substantially cheaper components.

IntelUser2000 - Thursday, July 25, 2019 - link

You mean 3D XPoint/Optane?Yes you can, with caveats. First, they only have 128Gbit(16GB) dies which are unnecessarily large for this purpose. Second, it'll end up being slower.

They'll need to split the space into two with 1GB being used as the buffer and the rest(15GB) being used as userspace caching. Then it'll become a slower SSD, but with 15GB Optane caching.

DanNeely - Thursday, July 25, 2019 - link

Potentially the mram will take up less space than the capacitors. The gallery Iinked shows a Samsung consumer 860 next to an enterprise 883 drive. The 6 super caps on the latter take up about as much PCB space as a flash chip or 2 ram chips. The MRAM chip shown in the article appears to be the same size as a standard DRAM; meaning that adding it and dropping the supercaps would free a bit of PCB space. If the MRAM could be stacked with the DRAM POP style it'd allow power loss protection without any extra board area. Probably not a huge issue in the 2.5" segment; but m.2 and various server focused high density stick drives are a lot more cramped for space.https://www.anandtech.com/Gallery/Album/6812#5

Santoval - Thursday, July 25, 2019 - link

(STT-)MRAM is much faster than 3D XPoint. It makes little sense to use 3D XPoint as a non volatile cache. 3D XPoint has a latency in the low μs (microsecond) range, while MRAM has a latency in the low to mid ns (nanosecond) range, depending on its type and capacity.MRAM of a small enough size is quite faster than DRAM and even rivals SRAM, though it is about 6 times denser than the latter. Thus it can even be used as a non volatile CPU cache. (STT-)MRAM is ideal as an SSD cache.

Guspaz - Thursday, July 25, 2019 - link

When it comes to storage (and not memory), I have a feeling that a 128 gigabit 3D XPoint read/write cache would outperform a 1 gigabit MRAM cache simply because how little data can fit in a 1 gigabit cache.Samus - Friday, July 26, 2019 - link

XPoint is also a power whore. Although we don't have data on STT-MRAM yet, judging by its footprint, it likely doesn't use much more power than DRAM. A lot of the surface area of XPoint is partially for heat dissipation (and the packaging has a ton of interconnects)BMNify - Saturday, July 27, 2019 - link

everspin mram can use less power than dram as it does not need the extra refresh logic, the slowest 45 nm QSPI consumer version does 52Megabyte/s read and write 20 year retension and unlimited writes at 35ns latencys, if phisons uses the ip directly then they can also uses the faster sram type latencies directly and stack them into any wide HBM format they like....DanNeely - Thursday, July 25, 2019 - link

You included figure 2 twice.