Samsung Ships First Commercial Embedded MRAM (eMRAM) Product

by Anton Shilov on March 6, 2019 4:00 PM EST

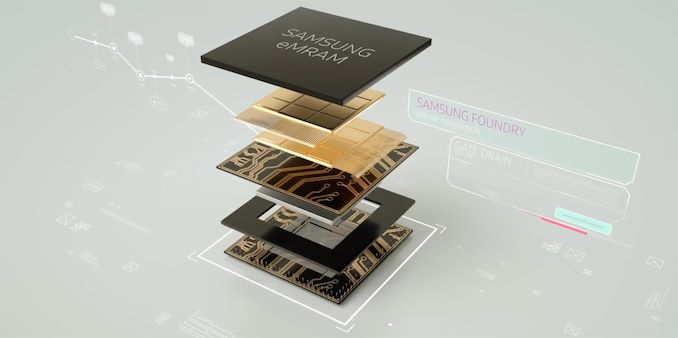

Samsung today announced that it has started mass production of its first commercial embedded Magnetic Random Access Memory (eMRAM). Made using its 28FDS (28nm FD-SOI) process technology, the eMRAM module promises to offer higher performance and endurance when compared to eFlash. Furthermore it can be integrated into existing chips, according to the manufacturer.

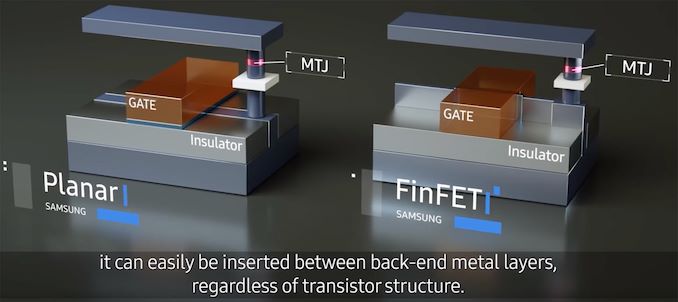

Magneto resistive RAM uses a resistance-based method that determines what data is stored in a cell, which in turn is based on reading the orientation of two ferromagnetic films separated by a thin barrier. Samsung calls this process Magnetic Tunnel Junction, or MTJ.

MRAM is one of the highest-performing and most durable non-volatile memory technologies currently exists. Because its eMRAM does not require an erase cycle before writing data, it is 1,000 times faster than eFlash, Samsung says. It also uses lower voltages when compared to eFlash, and therefore consumes around 1/400th the energy during writing process, according to the maker.

On the flip side, however, MRAM’s density and capacity both fall far short of 3D XPoint, DRAM, and NAND flash, which greatly reduces its addressable markets. Samsung is not formally disclosing the capacity of its new eMRAM module; the company is only saying that it yet has to tape out a 1 Gb eMRAM chip in 2019, which strongly suggests that the current offering has a lower capacity.

Made using Samsung’s 28FDS process technology, Samsung's eMRAM module can be integrated in the back-end of a chip's manufacturing process by adding three additional masks. As a result, the module does not necessarily depend on what front-end manufacturing technology is used, allowing it to be inserted into chips produced using bulk, FinFET, or FD-SOI fabrication processes.

Given its limited capacity, Samsung says that the module is primarilly aimed for use in microcontrollers, chips for IoT, and AI (neural network, machine learning, etc.) applications.

Meanwhile, Samsung says that it will keep expanding its embedded non-volatile memory offerings going forward. Among the upcoming options is its 1 Gb eMRAM test chip, whose tape-out is scheduled for later this year. Farther down the line still, Samsung is also planning to make eMRAM using its 18FDS process, as well as more advanced FinFET-based nodes.

Related Reading:

- IBM And Everspin Announce 19TB NVMe SSD With MRAM Write Cache

- Seagate Demos New SSD Features And Prototypes At FMS

- Everspin Announces New MRAM Products And Partnerships

- MRAM Developer Day, GlobalFoundries Keynote Live Blog

Source: Samsung

25 Comments

View All Comments

peevee - Wednesday, March 6, 2019 - link

How does it compare with eMRAM from Globalfoundries?eastcoast_pete - Wednesday, March 6, 2019 - link

Interesting launch! MRAM is (at least right now) really interesting in situations where you want to be able to write and re-write data many times to non-volatile solid storage; current NAND flash still has significant limits on the number of write-erase-rewrite cycles. Couple that with the (theoretical) speed advantage, and MRAM could be attractive as initial fast, non-volatile storage for digital photography and burst/high-speed video. For example, MRAM integrated into with the CMOS sensor circuitry to store RAW files.danielfranklin - Wednesday, March 6, 2019 - link

Usually the more i think about newer tech like this the more use cases i come up with, im really struggling to do that here though.Sure there are some very specific industrial cases where writes are through the roof but data sizes are small, but in a world where 3D XPoint is going to enter 2nd generation soon and will likely continue to scale well moving forward.

When DRAM is always going to be so much faster and a simply cap can provide the power to backup to flash when required, i just dont see many use cases.

saratoga4 - Wednesday, March 6, 2019 - link

>Usually the more i think about newer tech like this the more use cases i come up with, im really struggling to do that here though.It is a replacement for embedded flash and especially embedded NOR flash, which is in almost every embedded device. Huge market for this stuff, just not thing you are likely to be aware of.

>Sure there are some very specific industrial cases where writes are through the roof but data sizes are small, but in a world where 3D XPoint is going to enter 2nd generation soon and will likely continue to scale well moving forward.

XPoint cannot be used for these applications due to fabrication requirements. The alternative is usually NOR, which is really expensive and not scaling well to newer nodes.

flgt - Wednesday, March 6, 2019 - link

For an embedded microcontroller, dealing with NAND is a bit nasty without all the help from an OS and advanced memory controller (although the more advanced ones are starting to provide more support and blur the lines with application processors). NOR has good read performance for code storage but is slow to erase and write since you have to work in blocks. MRAM right now seems like a good replacement for EEPROM where you want a simple memory for logging or configuration. It’s simple and fast to write; write XX data at XX address.Processors like this will most likely be running out of SRAM (internal or external) or directly out of flash/MRAM, again since DRAM is a very powerful but overly complex memory. DRAM with flash is way too complex and not a competitor for these non-volatile applications, at least in the near term.

danielfranklin - Thursday, March 7, 2019 - link

Thanks, explains it well.The poor guy two posts below me though, i think hes a lost cause...

deil - Thursday, March 7, 2019 - link

1 Gb at starting point is not that bad.ANY database with transactions, where you need to update 4KB field milions of times per sec might want this.

Question if we can add it as "cache" for NAND/bufor for now or treat it as "swap" space for SQL/NON-SQL DB's

name99 - Thursday, March 7, 2019 - link

It’s for storage ON THE CHIP. So you don’t need an external DRAM, Flash or whatever.Of COURSE flash can be dense — it has 128 layers! Likewise DRAM has super tall caps! But those can’t be manufactured on the same chip as your logic...

That’s the win, get rid of one external chip, if you can.

Lord of the Bored - Wednesday, March 6, 2019 - link

Core memory on a chip. Everything old is new again.PeachNCream - Wednesday, March 6, 2019 - link

Endurance? Who cares about speed? If this is supposed to be some sort of replacement for NAND flash (including that awful QLC they're foisting on us as a solution to persistent storage to replace already awful TLC that replaced marginally acceptable MLC) then they need to talk about P/E cycle endurance. Since they're not, it's probably safe to say this is a bit like 5G, you can burn through those limited P/E cycles faster than ever before. Now pardon me while I go have a drink in the name of future lost data and dead consumer electronics components that are no longer useful thanks to soldered on storage failing only a few years into its service life. Peh!